# CH32V208 Datasheet

V2.6

#### Overview

The CH32V series is an industrial-grade general-purpose microcontroller based on the 32-bit RISC-V design of Qingke.

Designs such as fast interrupt entry greatly improve the interrupt response speed compared with the standard. CH32V208 is equipped with V4C core and adds memory protection function.

Reduce hardware division cycles. Product functions support 144MHz main frequency zero-wait operation, and this series of products integrates 2Mbps low-power Bluetooth

BLE communication module, 10M Ethernet MAC+PHY module, USB2.0 full-speed device+host/device interface, CAN controller, etc.

#### **Product Features**

#### I Core:

- Qingdao 32-bit RISC-V core, multiple instruction set combinations

- Fast programmable interrupt controller + hardware interrupt stack

- Branch prediction and conflict handling mechanism

- Single cycle multiplication, hardware division

- System clocked at 144MHz

#### I Memory:

- Can be configured with a maximum of 64KB volatile data storage

area SRAM Can be configured with 480KB program storage

area CodeFlash (zero wait application area + non-zero wait data area)

- 28KB system boot program storage area BootLoader 128B system non-volatile configuration information storage area

- 128B user-defined information storage area

I Power management and low power

consumption: - System power supply

VDD rated: 3.3V - GPIO unit independent power supply

VIO rated: 3.3V - Low power consumption mode: sleep, stop, standby

- VBAT power supply independently powers RTC and backup registers

# I System clock, reset

- Built-in factory-trimmed 8MHz RC oscillator

- Built-in 40KHz RC oscillator

- Built-in PLL, optional CPU clock up to 144MHz External support for 32MHz high-speed oscillator

- External support 32.768KHz low-speed oscillator

- Power-up/power-down reset, programmable voltage monitor

I Real-time clock RTC: 32-bit independent timer I 1 set of

8-way general-purpose DMA controller

- 8 channels, support ring buffer management

- Support TIMx/ADC/USART/I2C/SPI

I 2 sets of operational amplifiers and comparators: connected to ADC

and TIMx I 1 set of 12-bit analog-to-digital conversion ADC

-Analog input range: VSSAÿVDDA - 16

external signals + 2 internal signal channels

- On-chip temperature sensor

- Dual ADC conversion mode

I 16 TouchKey channel detection I Multiple

#### sets of timers

- 1 16-bit advanced timer with dead-band control and emergency

Brake, providing PWM complementary output for motor control

- 3 16-bit general-purpose timers providing input capture/output ratio

Comparison/PWM/pulse counting and incremental encoder input

- 1 x 32-bit general-purpose timer

- 2 watchdog timers (independent and windowed)

- System time base timer: 64-bit counter

I Multiple communication interfaces:

- 4 USART interfaces

- 2 I2C interfaces (support SMBus/PMBus)

- 2 SPI interfaces

- USB2.0 full-speed device interface (full speed and low speed)

- USB2.0 full-speed host/device interface

- 1 CAN interface (2.0B active)

- Built-in 10M PHY transceiver

- Bluetooth Low Energy BLE5.3 I

Fast GPIO Ports - 53 I/O ports,

mapped to 16 external interrupts

I Security features: CRC calculation unit, 96-bit chip unique ID I Debug

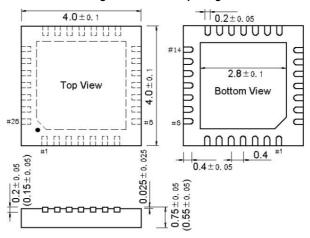

mode: Serial 2-wire debug interface I Package: LQFP

and QFN

# **Chapter 1 Product Description**

The CH32V series products are industrial-grade general-purpose enhanced MCUs designed based on the 32-bit RISC-V instruction set and architecture.

Resources are divided into general, connection, wireless and other categories. They are divided into packaging categories, peripheral resources and quantity, number of pins, device characteristics, etc.

The differences in height extend to each other, but they remain compatible with each other in terms of software, functions, and hardware pin configuration, providing users with a better understanding of the product development process.

Product iteration and rapid application provide freedom and convenience.

Please refer to the data sheet for device characteristics of this series of products.

For detailed information on the product peripheral function description, usage methods, register configuration, etc., please refer to "CH32FV2x\_V3xRM".

Both the data sheet and reference manual can be downloaded from Qinheng's official

website: www.wch.cn. Related information about the RISC-V instruction set and architecture can be downloaded from the "http://riscv.org" website.

This manual is the data sheet for the CH32V208 series products. For the V203 series, please refer to "CH32V203DS0", for the V303\_305\_307 series, please refer to "CH32V307DS0".

Table 1-1 Product series overview

| 1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986   1986      | Small and medium c                                  | apacity general purpose                                  | Large-capacity                                            | universal type (V303)                                                                                      | Connected type (V305) Ir                                                                                             | terconnected type (V307                                                                                                               | ) Wireless type (V208)                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 10K SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (V20                                                | 3) Highland barley V4B                                   |                                                           | Highl                                                                                                      | and Barley V4F                                                                                                       | 1                                                                                                                                     | Highland Barley V4C                                                                        |

| 2*ADC(TKey) 2*DAC 2*ADC(TKey) 2*DAC 2*DAC 4*ADTM ADTM ADTM ADTM 2*DAC 3*GPTM 3*GPTM ADTM 2*BCTM 3*GPTM 3*GPTM ADTM 2*BCTM 3*GPTM 2*BCTM 3*GPTM | 32K Flash 64K                                       | Flash 128K Flash 256K Fl                                 | ash 128K Flash 256K                                       | Flash 128K Flash                                                                                           |                                                                                                                      |                                                                                                                                       |                                                                                            |

| 2'ADC(TKey) 2'ADC(TKey) 2'DAC 2'DAC 2'DAC 4'ADTM 4'ADTM ADTM 2'ADC(TKey) 2'DAC 4'ADTM ADTM ADTM ADTM ADTM ADTM ADTM 3'GPTM 3'GPTM ADTM 3'GPTM ADTM 3'GPTM 3'GPTM 3'GPTM 3'GPTM 3'GPTM 3'GPTM ADTM 2'BCTM 3'SPI(2'12S) | 10K SRAM                                            | 20K FOR SHAME                                            | 32K SRAM                                                  | 64K SRAM                                                                                                   | 32K SRAM                                                                                                             | 64K SRAM                                                                                                                              | 64K SRAM                                                                                   |

| ETH-1000MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ADTM 3*GPTM 2*USART SPI 2C USBD USBFS CAN RTC 2*WDG | ADTM 3*GPTM 4*USART 2*SPI 2*12C USBD USBFS CAN RTC 2*WDG | 2°DAC ADTM 3°GPTM 3°USART 2°SPI 2°12C USBFS CAN RTC 2°WDG | 2*DAC  4*ADTM  4*GPTM  2*BCTM  8*USART/UART  3*SPI(2*12S)  2*12C  USBFS  CAN  RTC  2*WDG  4*OPA  RNG  SDIO | 2*DAC  4*ADTM  4*GPTM  2*BCTM  5*USART/UART  3*SPI(2*12S)  2*12C  OTG_FS  USBHS(+PHY)  2*CAN  RTC  2*WDG  4*OPA  RNG | 2°DAC  4°ADTM  4°GPTM  2°BCTM  8°USART/UART  3°SPI(2°12S)  2°12C  OTG_FS  USBHS(+PHY)  2°CAN  RTC  2°WDG  4°OPA  RNG  SDIO  FSMC  PAD | ADTM 3*GPTM GPTM(32) 4*USART/UART 2*SPI 2*12C USBD USBFS CAN RTC 2*WDG 2*OPA ETH-10M(+PHY) |

Note: The number or functions of some peripherals in the same category may be limited by the package. Please confirm the product package when selecting.

abbreviation

ADTM: Advanced Timer TKey: Touch key USBFS: Full-Speed Host/Device Controller

GPTM: General purpose timer OPA: operational amplifier, comparator USBHS: High Speed Host/Device Controller

GPTM(32): 32-bit general purpose timer RNG: random number generator

BCTM: basic timer USBD: Full-Speed Device Controller

Table 1-2 Kernel comparison overview

| Features | Instruction Set | hardware<br>Stack<br>series | interrupt<br>Nested<br>series | fast Interrupt Number of channels | integer<br>division<br>cycle | vector table<br>model         | Extensions | Memory<br>Protect |

|----------|-----------------|-----------------------------|-------------------------------|-----------------------------------|------------------------------|-------------------------------|------------|-------------------|

| V4B      | IMAC            | 2                           | 2                             | 4                                 | 9 Addres                     | s or instruction support None |            |                   |

| V4C      | IMAC            | 2                           | 2                             | 4                                 | 5 Addres                     | s or command support standard |            |                   |

| V4F      | IMAFC           | 3                           | 8                             | 4                                 | 5 Addres                     | s or command support standard |            |                   |

$Note: For \ relevant \ information \ about \ the \ kernel, \ please \ refer \ to \ the \ QingKeV4 \ microprocessor \ manual \ "QingKeV4\_Processor\_Manual".$

# **Chapter 2 Specifications**

The CH32V208 series is a 32-bit RISC core MCU designed based on the RISC-V instruction architecture, with an operating frequency of 144MHz and built-in high-speed storage.

The system architecture has multiple buses working synchronously, providing rich peripheral functions and enhanced I/O ports.

It also includes functions such as ADC module, multiple timers, multi-channel touch button capacitance detection (TKey), and standard and dedicated communication interfaces:

I2C, SPI, USART, CAN controller, USB2.0 full-speed host/device controller, USB2.0 full-speed device controller, Bluetooth low energy, etc.

The product has a rated operating voltage of 3.3V and an operating temperature range of -40ÿÿ85ÿ industrial grade. It supports a variety of power-saving working modes to meet the needs of production product low power application requirements. Each model in the series of products differs in terms of resource allocation, number of peripherals, peripheral functions, etc. You can choose according to your needs.

### 2.1 Model comparison

Table 2-1 Wireless product resource allocation

|           |                    | Product number |         | CH32V20                 | 8       |                 |  |  |  |  |

|-----------|--------------------|----------------|---------|-------------------------|---------|-----------------|--|--|--|--|

| Resourc   | e differences      |                | GB      | СВ                      | RB      | WB              |  |  |  |  |

|           | Number of chip     | pins           | 28      | 48                      | 64      | 68              |  |  |  |  |

|           | Flash memory (byte | (1)<br>s)      | 128K(2) | 128K(2)                 | 128K(2) | 128K(2)         |  |  |  |  |

|           | SRAM (bytes)       |                | 64K(2)  | 64K(2)                  | 64K(2)  | 64K(2)          |  |  |  |  |

|           | Number of GPIO     | ports          | 21      | 37                      | 49      | 53              |  |  |  |  |

|           | GPIO Power S       | upply          |         | Shared with VDD         |         | Independent VIO |  |  |  |  |

|           | Advanced (16-      | bit) General   | 1       | 1                       | 1 1     |                 |  |  |  |  |

| Certainly | (16-bit) Genera    | I (32-bit)     | 3       | 3                       | 3       | 3               |  |  |  |  |

| hour      | Watchdog Sys       | tem            | 1       | 1                       | 1 1     |                 |  |  |  |  |

| Device    | Timeba             | ase (24-       | 2       | 2                       | 2       | 2               |  |  |  |  |

|           | bit)               |                |         | supp                    | port    |                 |  |  |  |  |

|           | RTC                |                |         | support                 |         |                 |  |  |  |  |

|           | ADC/TKey (nu       |                | 8@1     | 16@1                    | 16@1    | 16@1            |  |  |  |  |

|           | amplifier, compara | itor           | OPA2    | 2                       | 2       | 2               |  |  |  |  |

|           | USART/UAF          | RT             | 2       | 4                       | 4       | 4               |  |  |  |  |

|           | SPI                |                | 1       | 2                       | 2       | 2               |  |  |  |  |

| Pass      | 2C                 |                | 1       | 2                       | 2       | 2               |  |  |  |  |

| letter    | CA                 | N              | 1       | 1                       | 1       | 1               |  |  |  |  |

| catch     | USB(FS)            | USBD           | 1       | 1                       | 1       | 1               |  |  |  |  |

| mouth     | U3B(F3)            | USBHD          | 1       | 1                       | 1       | 1               |  |  |  |  |

|           | Ethernet           |                | 10M     | -                       | 10M     |                 |  |  |  |  |

|           | BE 5.3             |                |         | supp                    | port    |                 |  |  |  |  |

|           | CPU main           |                |         | Maxÿ14                  | MHz     |                 |  |  |  |  |

|           | frequency Rat      | ed             |         | 3.3V                    | v       |                 |  |  |  |  |

|           | voltage Opera      | iting          |         | Industrial grade: -40ÿÿ | 85ÿ     |                 |  |  |  |  |

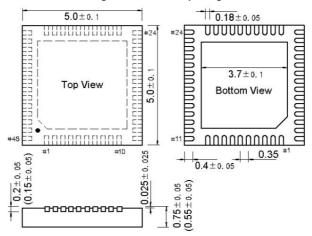

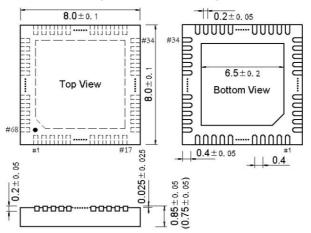

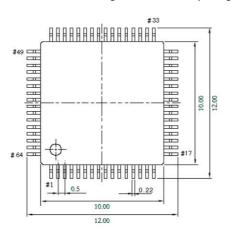

|           | temperature F      | ackage type    | QFN28   | QFN48                   | LQFP64M | QFN68           |  |  |  |  |

Note: 1. The flash memory byte represents the zero wait operation area ROWAIT. V208 the size is 480K- ROWAIT

FLASH+64K SRAM), (144K 2.128KProducts with non-zero wait area support user-selected word configurations as (128K FLASH+64K SRAM 208 FLASH+48K SRAM), (160K FLASH+32K SRAM) one of several combinations.

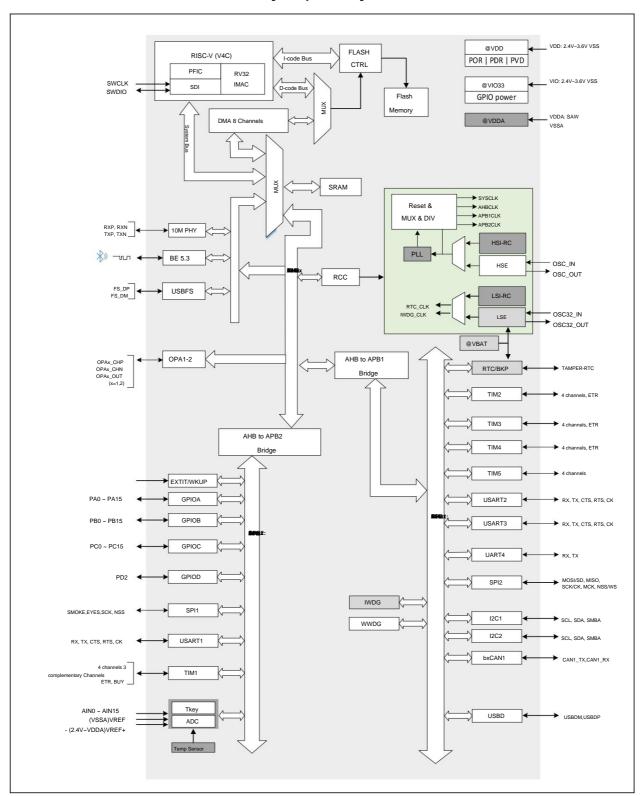

#### 2.2 System Architecture

The microcontroller is designed based on the RISC-V instruction set. In its architecture, the core, arbitration unit, DMA module, SRAM storage and other parts interact through multiple sets of buses. The design integrates a general DMA controller to reduce the burden on the CPU and improve access efficiency. It applies a multi-level clock management mechanism to reduce the operating power consumption of peripherals. It also has a data protection mechanism, automatic clock switching protection and other measures to increase system stability. The figure below is a block diagram of the overall internal architecture of the series of products.

Figure 2-1 System block diagram

CH 3 2 V 208 Data Sheet http://wch.cn

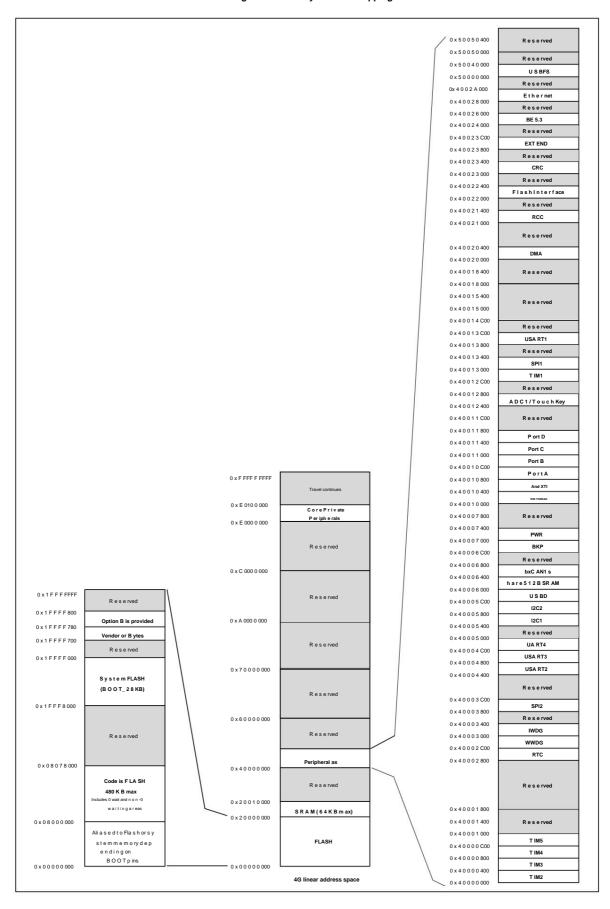

# 2.3 Memory Mapping Table

Figure 2-2 Memory address mapping

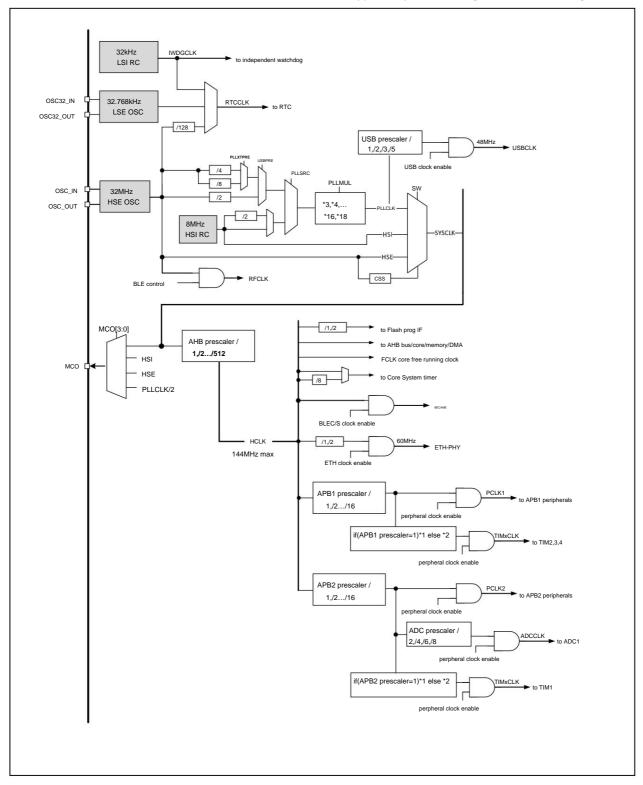

### 2.4 Clock Tree

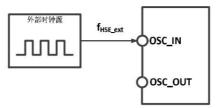

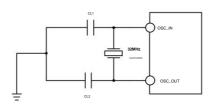

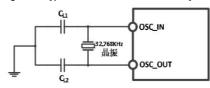

Four groups of clock sources are introduced into the system: internal high-frequency RC oscillator (HSI), internal low-frequency RC oscillator (LSI), external high-frequency oscillator (HSE), and external low-frequency oscillator (LSE). Among them, the low-frequency clock source provides the clock reference for RTC and independent watchdog. The high-frequency clock source is directly or indirectly multiplied by PLL and output as the system bus clock (SYSCLK). The system clock is then provided by various pre-dividers to the AHB domain, APB1 domain, APB2 domain peripheral control clock and sampling or interface output clock. Some modules need to be directly provided by the PLL clock. Figure 2-3 Clock tree block diagram

Note: 1. When using this function, the CPU frequency must be 48MHz or 144MHz. 96MHz

When waking up, the system will automatically รีรีนีเปรีย โดยีนี้เล็กคนนี้เดินและนักสิโนกับเกิดสาร์เทียร์และรับเรื่อนี้เดินและนักเกิดสาร์เทียร์และรับเรื่อนให้ time, you need to select USBPRE=5DIV, and 240M, AHBPRE=2DIV, CPU 120M.

2. The external crystal or clock (HSE) of CH32V208 product is 32M. When using external crystal, no load capacitor is required and it is built-in.

#### 2.5 Function overview

#### 2.5.1 RISC-V4C Processor

RISC-V4C supports the IMAC subset of the RISC-V instruction set. The processor is managed in a modular manner, including units such as the fast programmable interrupt controller (PFIC), memory protection, branch prediction mode, and extended instruction support. Multiple external buses are connected to external unit modules to achieve interaction between external

functional modules and the core. The processor can be flexibly applied to microcontrollers in different scenarios with its minimalist instruction set, multiple working modes, and modular Design, such as small-area low-power embedded scenarios, high-performance application operating system

scenarios, etc. I Supports machine and user

privilege modes I Fast programmable interrupt controller

(PFIC) I Multi-level hardware interrupt

stack | Serial 2-wire debugging

interface I Standard memory protection

design I Static or dynamic branch prediction, efficient jump, conflict detection mechanism

I Custom extension directive

#### 2.5.2 On-chip memory and boot mode

Built-in maximum 64K bytes SRAM area for storing data, which will be lost after power failure. The specific capacity should correspond to the chip model. Built-in maximum 480K bytes program flash storage area (Code FLASH) for user application and constant data storage. It includes zero wait program running area and non-zero wait area. The specific size of the area corresponds to the chip model.

Built-in 28K bytes of system storage area (System FLASH) for system boot program storage (factory fixed bootloader). 128 bytes for system non-volatile configuration information storage area, 128 bytes for user selected word storage area. At startup, one of three boot modes can be selected through the boot pins (BOOT0 and BOOT1): I Boot from program flash memory I Boot from system memory I Boot from internal SRAM The bootloader is stored

in the system storage area, and the

contents of the program flash

storage area can be reprogrammed through USART1 and USB interface.

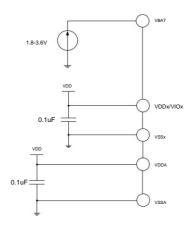

#### 2.5.3 Power Supply Solution

I VDD = 2.4ÿ3.6V: Powers some I/O pins and internal voltage regulator. I VIO = 2.4ÿ3.6V: Powers most I/O pins and Ethernet module, and determines the pin output high voltage amplitude. Normal

During operation, the VIO voltage cannot be higher than the VDD voltage.

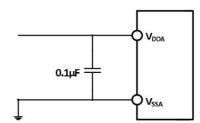

I VDDA = 2.4ÿ3.6V: Powers the analog parts of high-frequency RC oscillator, ADC, temperature sensor, DAC and PLL. The VDDA voltage must be the same as the VIO voltage (if VDD is powered off and VIO is powered, VDDA must be powered and consistent with VIO). When using the ADC, VDDA must not be less than 2.4V.

I VBAT = 1.8~3.6V: When VDD is turned off, (through the internal power switch) the RTC, external low-frequency oscillator and rear Power supply for the backup register. (Note the VBAT power supply)

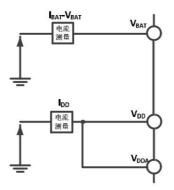

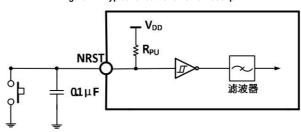

# 2.5.4 Power supply monitor This

product integrates a power-on reset (POR)/power-down reset (PDR) circuit. This circuit is always in working state to ensure that the system works when the power supply exceeds 2.4V; when VDD is lower than the set value threshold (VPOR/PDR), the device is placed in the reset state without using an external reset circuit. In addition, the system is equipped with a programmable voltage monitor (PVD), which needs to be turned on through software to compare the voltage of the VDD power supply with the set threshold VPVD. Turn on the corresponding edge interrupt of PVD, and you can receive an interrupt notification when VDD drops to the PVD threshold. Refer to Chapter 4 for the values of VPOR/PDR and VPVD.

#### 2.5.5 After the voltage regulator

is reset, the regulator automatically turns on. There are three operating modes according to

the application. I On mode: normal operation, providing stable core power supply I Low

power mode: when the CPU enters stop mode, you can select The regulator operates with low power

consumption. Shutdown mode: When the CPU enters standby mode, the regulator automatically switches to this mode. The output of the voltage regulator is in a high-impedance of the consumption.

The power supply to the circuit is cut off and the voltage regulator is in a zero consumption state

The voltage regulator is always in the on mode after reset, and is turned off in the shutdown mode in standby mode. At this time, it is a high-impedance output.

#### 2.5.6 Low Power Mode The

system supports three low power modes, which can be selected to achieve the best balance between low power consumption, short startup time and multiple

wake-up events. I

Sleep mode in sleep mode, only the CPU clock stops, but all peripheral clocks are powered normally and the peripherals are in working state. This mode is the shallowest low power mode, but can achieve the

fastest wake-up. Exit condition: any interrupt or

wake-up event. I Stop

mode In this mode, FLASH enters low power mode, and PLL, HSI RC oscillator and HSE crystal oscillator are turned off. While maintaining SRAM and Stop mode can achieve the lowest power consumption without losing the register contents.

Exit conditions: any external interrupt/event (EXTI signal), external reset signal on NRST, IWDG reset, where EXTI signal

The signals include one of 16 external I/O ports, PVD output, RTC alarm, Ethernet wake-up signal or USB wake-up signal.

I Standby mode In

this mode, the main LDO of the system is turned off, and the low-power LDO supplies power to the wake-up circuit. All other digital circuits are powered off, and FLASH is in a power-off state. Waking up the system from standby mode will generate a reset and SBF (PWR\_CSR) will be set. After waking up, query the SBF status to know the low power consumption mode before waking up. SBF is cleared by the CSBF (PWR\_CR) bit. In standby mode, the contents of the 32KB SRAM can be retained (depending on the planned configuration before sleep).

and the contents of the back-up registers are retained. Exit conditions: any external event (EXTI signal), external reset signal on NRST, IWDG reset, a rising edge on the WKUP pin, where the EXTI signal includes one of the 16 external I/O ports, RTC alarm clock, wake-up on Ethernet signal or USB wake-up signal.

#### 2.5.7 CRC (Cyclic Redundancy Check) calculation unit The CRC

(Cyclic Redundancy Check) calculation unit uses a fixed polynomial generator to generate a CRC code from a 32-bit data word. In numerous applications, CRC-based technology is used to verify the consistency of data transmission or storage. Within the scope of the EN/IEC 60335-1 standard, which provides a means of detecting flash memory errors, a CRC calculation unit can be used to calculate the signature of the software in real time and compare it with the signature generated when the software is linked and generated.

# 2.5.8 Fast Programmable Interrupt Controller (PFIC) The

product has a built-in Fast Programmable Interrupt Controller (PFIC), which supports up to 255 interrupt vectors and provides flexible interrupt management functions with minimal interrupt delay. The current product manages 8 core private interrupts and 88 peripheral interrupt management, and other interrupt sources are reserved. The registers of the PFIC are accessible in both user

q

and machine privileged modes. I 2

independently maskable interrupts I Provide a

non-maskable interrupt NMI I Support hardware interrupt stack (HPE),

no instruction overhead I Provide 4-way table-

free interrupts (VTF) I Vector table supports address

or instruction mode I Interrupt nesting depth can be

Configure up to level 2 I to support the interrupt tail link function

#### 2.5.9 External Interrupt/Event Controller (EXTI) The

external interrupt/event controller contains a total of 19 edge detectors for generating interrupt/event requests. Each interrupt line can be independently configured for its trigger event (rising edge or falling edge or both edges) and can be independently masked; the pending register maintains the status of all interrupt requests. EXTI can detect a pulse width smaller than the internal APB2 clock period. Up to 53 general-purpose I/O ports can be optionally connected to 16 external interrupt lines.

#### 2.5.10 General DMA Controller

The system has a built-in general DMA controller that manages 8 channels, flexibly handles high-speed data transfers between memory and memory, peripherals and memory, and memory and peripherals, and supports the ring buffer mode. Each channel has a dedicated hardware DMA request logic to support one or more peripherals' access requests to the memory, and can configure access priority, transfer length, source address and destination address of the transfer, etc.

DMA is used for major peripherals including: general/advanced/basic timers TIMx, ADC, USART, I2C, SPI.

Note: DMA accesses GRU System after arbitration by the arbitrator.

#### 2.5.11 Clock and startup

system clock source HSI is enabled by default. When no clock is configured or after reset, the internal 8MHz RC oscillator is used as the default CPU clock, and then an external 32MHz clock or PLL clock can be selected. When the clock safety mode is turned on, if the HSE is used as the system clock (directly or indirectly) and an external clock failure is detected at this time, the system clock will automatically switch to the internal RC oscillator, and the HSE and PLL will automatically shut down; for the low In power consumption mode, the system will automatically switch to the internal RC oscillator after waking up. If the clock interrupt is enabled,

the software can receive the corresponding interrupt. Multiple prescalers are used to configure the frequency of AHB. The high-speed APB (APB2) and low-speed API

The frequency is 144MHz, refer to the clock tree block diagram in Figure 2-3.

### 2.5.12 RTC (Real Time Clock) and Backup Register

The RTC and backup registers are in the backup power supply area within the system. They are powered by VDD when VDD is valid. When VDD is invalid, the internal Switch to be powered by the VBAT pin.

The RTC real-time clock is a set of 32-bit programmable counters, and the time base supports 20-bit prescaler for measurement over a longer period of time. The clock reference source is a high-speed external clock divided by 128 (HSE/128), an external crystal low-frequency oscillator (LSE) or an internal low-power RC oscillator (LSI). LSE also has a backup power supply area, so when LSE is selected as the RTC time base, the RTC settings and time can remain unchanged after the system is reset or wakes up from standby mode. The backing register contains up to 42 16-bit

registers, which can be used to store 84 bytes of user application data. This data is on standby

After waking up, or when the system is reset or the power is reset, it can continue to maintain. When the intrusion detection function is turned on, once the intrusion detection signal is valid, all contents in the backup register will be cleared.

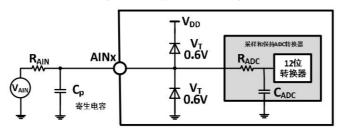

#### 2.5.13 ADC (analog/digital converter) and touch key capacitance detection (TKey)

The product has a built-in 12-bit analog/digital converter (ADC), which can share up to 16 external channels and 2 internal channels for sampling. The programmable channel sampling time can realize single, continuous, scan or intermittent conversion, and supports dual ADC conversion mode. The analog watchdog function allows very accurate monitoring of one or more selected channels for monitoring channel signal voltage. Supports external event trigger conversion, and the trigger source includes the internal signal of the on-chip timer and the external pin. Supports the use of DMA operation.

The ADC internal channel sampling includes one built-in temperature sensor sampling and one internal reference power supply sampling. The temperature sensor generates a voltage that changes linearly with temperature. The temperature sensor is internally connected to the IN16 input channel, which converts the sensor output to a digital value. The

touch button capacitance detection unit provides up to 16 detection channels and multiplexes the external channels of the ADC module. The detection results are converted to output results through the ADC module, and the touch button status is identified through the user software.

#### 2.5.14 Timer and Watchdog

Timers in the system include advanced timers, general timers, basic timers, watchdog timers and system time base timers.

Different products in the series contain different numbers of timers, please refer to Table 2-2 for details.

Table 2-2 Timer comparison

| Time              | r resolution cou    | ınt type time ba | ase                   |                                           | DMA           | function                                                                                |

|-------------------|---------------------|------------------|-----------------------|-------------------------------------------|---------------|-----------------------------------------------------------------------------------------|

| advanced<br>timer | TIM1                | 16 bit           | up<br>down<br>up/down | APB2 time domain 16-bit frequency divider | support       | PWM complementary output, single pulse output input capture Output Compare Timing Count |

| General<br>timer  | TIM2 TIM3 TIM4 TIM5 | 16 bit<br>32 bit | up<br>down<br>Up/Down | APB1 Time Domain                          | support       | input capture  Output Compare  Timing count                                             |

| Window            | watchdog 7 bit      | down             |                       | APB1 time domain 4 crossovers             | not support   | timing Reset system (normal operation)                                                  |

| Indepen           | dent watchdog       | 12-bit down      |                       |                                           | •             |                                                                                         |

| System tir        | ne base timer 6     | 4 bit up or dow  | n                     | SYSCLK or<br>SYSCLK/8                     | Timing is not | supported                                                                               |

#### I Advanced control timer The

advanced control timer is a 16-bit auto-loading up/down counter with a 16-bit programmable prescaler. Except for finishing

In addition to the general purpose timer function, it can be viewed as a three-phase PWM generator assigned to 6 channels, with complementary PWM with dead zone insertion.

Output functions that allow the timer to be updated after a specified number of counter cycles for repeated counting cycles, brake functions, etc. Advanced control

Many functions of timers are the same as general timers, and the internal structure is also the same, so advanced control timers can be linked through timers

The function operates in conjunction with other TIM timers to provide synchronization or event chaining capabilities.

### I General timer

The general-purpose timer is a 16-bit or 32-bit autoloading up/down counter with a programmable 16-bit prescaler

And 4 independent channels, each channel supports input capture, output compare, PWM generation and single pulse mode output.

The timer chaining feature works with the advanced control timer to provide synchronization or event chaining capabilities. In debug mode, the counter can

The PWM outputs are disabled, thus turning off the switches controlled by these outputs. Any general purpose timer can be used to generate PWM

output. Each timer has an independent DMA request mechanism. These timers are also capable of processing incremental encoder signals and can also handle 1

Digital outputs to 3 Hall sensors.

### I Independent watchdog

The independent watchdog is a free-running 12-bit down counter that supports 7 frequency division factors. consists of an internal independent 40KHz

An RC oscillator (LSI) provides the clock; because the LSI is independent of the main clock, it can operate in stop and standby modes. IWDG in main process

can work completely independently from the program and therefore be used to reset the entire system in the event of a problem or as a free timer for applications

The program provides timeout management. The watchdog can be configured to be software or hardware enabled through the option byte. In debug mode, the counter can

is frozen.

### I Window watchdog

The window watchdog is a 7-bit down counter and can be set to free running. Can be used to reset the entire system in the event of a problem system. It is driven by the main clock and has an early warning interrupt function; in debug mode, the counter can be frozen.

#### I System time base timer The

Qingke microprocessor core comes with a 64-bit optional increment or decrement counter, which is used to generate SYSTICK exceptions (exception number: 15). It can be used exclusively in real-time operating systems to provide a "heartbeat" rhythm for the system, and can also be used as a standard 64-bit counter. It has automatic reload function and programmable clock source.

#### 2.5.15 Communication Interface

#### 2.5.15.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The product provides 3 sets of universal synchronous/asynchronous receivers and transmitters (USART1, USART2, USART3), and 1 set of universal asynchronous receivers and transmitters (UART4). Supports full-duplex asynchronous communication, synchronous one-way communication and half-duplex single-line communication. It also supports LIN (local interconnection network), is compatible with ISO7816 smart card protocol and IrDA SIR ENDEC transmission codec specification, and modem (CTS/RTS hardware flow control) operate. Also allows multi-processor communication. It uses a fractional baud rate generator system and supports DMA operation for continuous communication.

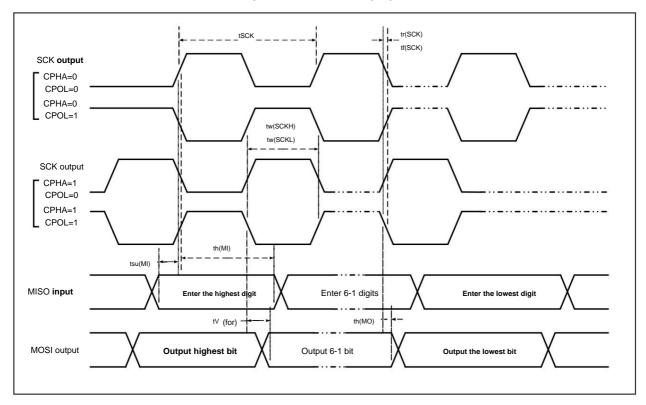

#### 2.5.15.2 Serial Peripheral Interface (SPI)

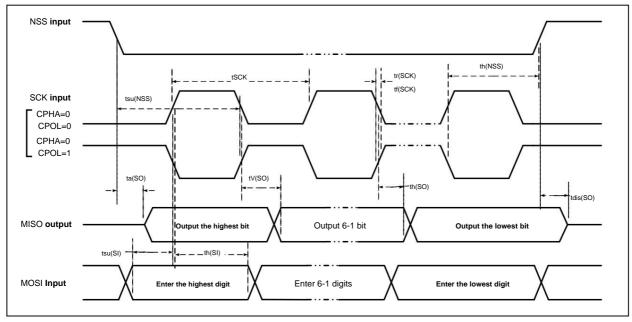

Up to 2 sets of serial peripheral SPI interfaces, providing master or slave operation and dynamic switching. Supports multi-master mode, full-duplex or half-duplex synchronous transmission, and supports basic SD card and MMC modes. Programmable clock polarity and phase, data bit width provides 8 or 16-bit selection, hardware CRC generation/check for reliable communication, supports DMA operation for continuous communication.

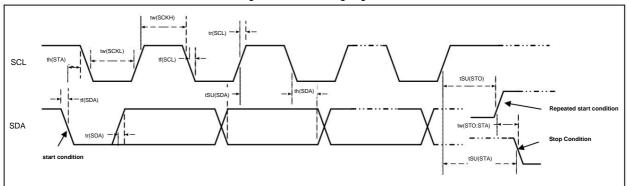

#### 2.5.15.3 I2C bus has up to 2

I2C bus interfaces, which can work in multi-master mode or slave mode and complete all I2C bus-specific timing, protocols,

Arbitration, etc. Supports both standard and fast communication speeds and is compatible with SMBus2.0.

The I2C interface provides 7-bit or 10-bit addressing and supports dual slave addressing in 7-bit slave mode. Built-in hardware CRC generator It can use DMA operation and supports SMBus bus version 2.0/PMBus bus.

### 2.5.15.4 Controller Area Network (CAN)

The CAN interface is compatible with specifications 2.0A and 2.0B (active), with a baud rate of up to 1Mbits/s and supports time-triggered communication. It can receive and send standard frames with 11-bit identifiers, as well as extended frames with 29-bit identifiers. It has 3 send mailboxes and 2 3-level deep receive FIFOs. There are only 14

settable filters for a CAN controller product with 1 group, and it shares a dedicated 512-byte SRAM memory with the USBD module for data transmission and reception. When USBD and CAN are used at the same time, in order to prevent access conflicts to SRAM, USBD can only use the lower 384-byte space.

### 2.5.15.5 Universal Serial Bus (USBD)

The product has a built-in USB2.0 full-speed controller and complies with the USB2.0 Fullspeed standard. USBD provides 16 configurable USB device endpoints, supports low-speed devices and full-speed devices, supports control/bulk/synchronous/interrupt transmission, double buffer mechanism, USB suspend/resume operation, and has standby/wake-up function. The USB-specific 48MHz clock is directly generated by the internal main PLL frequency division.

#### 2.5.15.6 Universal Serial Bus USB2.0 Full Speed Host/Device Controller (USBFS)

USB2.0 Full-Speed Host Controller and Device Controller (USBFS) follows the USB2.0 Fullspeed standard. Provides 16 configurable USB device endpoints and a set of host endpoints. Supports control/batch/synchronous/interrupt transfer, double buffer mechanism, USB bus suspend/resume operation, and provides standby/wake-up function. The dedicated 48MHz clock of the USBFS module is directly generated by the internal main PLL frequency division (PLL must be 144MHz or 96MHz or 48MHz).

## 2.5.16 General Purpose Input/Output Interface (GPIO)

The system provides 4 groups of GPIO ports with a total of 53 GPIO pins. Each pin can be configured by software as an output (push-pull or open-drain), input (with or without pull-up or pull-down), or a multiplexed peripheral function port. Most GPIO pins are shared with multiplexed digital or analog peripherals. Except for ports with analog input functions, all GPIO pins have high current passing capabilities. Provides a locking mechanism to freeze IO configuration,

This is to avoid accidental writing to I/O registers.

Most of the IO pin power in the system is provided by VIO. By changing the VIO power supply, the high value of the IO pin output level will be changed to adapt to the external Communication interface level. Please refer to the pin description for specific pins.

# 2.5.17 Operational Amplifier Comparator (OPA)

The product has two built-in op amp/comparator groups, which are internally selected to be associated with ADC and TIMx peripherals. Both input and output can be changed by changing the configuration

It supports amplifying external analog small signals and sending them to ADC to realize small signal ADC conversion.

No. comparator function, the comparison result is output by GPIO or directly connected to the input channel of TIMx.

### 2.5.18 Serial 2-wire debug interface (SDI Serial Debug Interface)

The core has a serial 2-wire debug interface (SDI), including SWDIO and SWCLK pins.

The test interface pin function is turned on, and SDI can be turned off as needed after the main program is run.

# **Chapter 3 Pin Information**

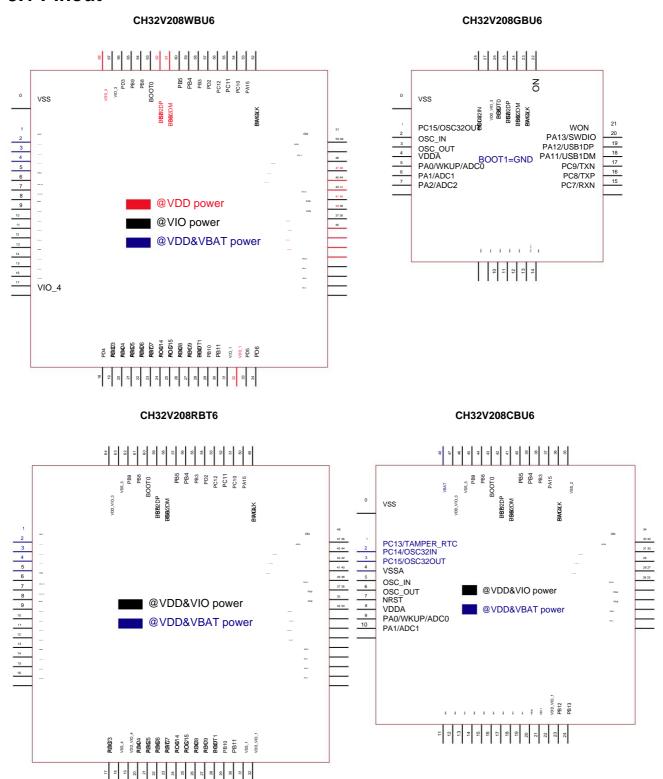

# 3.1 Pinout

# 3.2 Pin Description

Table 3-1 Pin Definition

Note that the pin function descriptions in the following table are for all functions and do not involve specific model products. Peripheral resources vary between different models. Please confirm whether this function is available according to the product model resource table before checking

| Note that the |        | umber | -    | ng table are for all fullcuons and do no | t invoive specific in | Ø                | s. reripheral resources vary bet | ween different models. Please confirm whether this function is a | variable according to the product model resource table |

|---------------|--------|-------|------|------------------------------------------|-----------------------|------------------|----------------------------------|------------------------------------------------------------------|--------------------------------------------------------|

| QFI           | 128 QF | N48   | QI   | pin<br><sub>-N68</sub> name              | Pinout<br>type        | electricity flat | Main Function (After reset)      | Default multiplexing func                                        | ion remapping function (8)                             |

| 00            | 0      |       |      | vss                                      | Р                     | -                | vss                              |                                                                  |                                                        |

| - 48          | 1      |       | 1    | VBAT                                     | Р                     | -                | VBAT                             |                                                                  |                                                        |

|               | 1      | 2     | 2    | PC13-<br>TAMPER-RTC(2)                   | I/O -                 |                  | PC13(3)                          | TAMPER-RTC                                                       |                                                        |

| 28 2          | 3 3    |       |      | PC14-<br>OSC32_IN(2)                     | I/O/A -               |                  | PC14(3)                          | OSC32_IN                                                         |                                                        |

| 1             | 3 4    | 4     |      | PC15-<br>OSC32_OUT(2)                    | I/O/A -               |                  | PC15(3)                          | OSC32_OUT                                                        |                                                        |

| - 4 5         |        |       | 5    | VSSA                                     | Р                     | -                | VSSA                             |                                                                  |                                                        |

| 2 5           | 6 6    |       |      | OSC_IN                                   | I/A - C               | SC_II            | N                                |                                                                  |                                                        |

| 36            | 7 7    |       |      | OSC_OUT                                  | O/A -                 | osc_             | рит                              |                                                                  |                                                        |

| - 78          | 8      |       |      | NRST                                     | i                     | -                | NRST                             |                                                                  |                                                        |

| 9             |        |       | 9    | PC0                                      | I/O/A -               |                  | PC0                              | ADC_IN10                                                         |                                                        |

| 1             | 0 10   |       |      | PC1                                      | I/O/A -               |                  | PC1                              | ADC_IN11                                                         |                                                        |

| 1             | 1 11   |       |      | PC2                                      | I/O/A -               |                  | PC2                              | ADC_IN12                                                         |                                                        |

| 1             | 2 12   |       |      | PC3                                      | I/O/A -               |                  | PC3                              | ADC_IN13                                                         |                                                        |

| 48            | 13 13  |       |      | VDDA                                     | Р                     | -                | VDDA                             |                                                                  |                                                        |

| 59            | 14 14  | PA0-V | /KUP | I/O/A -                                  |                       |                  | PA0                              | WKUP/USART2_CTS ADC_IN0/TIM2_CH1(9) TIM2_ETR(9)/TIM5_CH1         | TIM2_CH1_2(9) TIM2_ETR_2(9)                            |

| 6 10          | 15 15  |       |      | PA1                                      | I/O/A -               |                  | PA1                              | USART2_RTS/ADC_IN1<br>TIM5_CH2/TIM2_CH2                          | TIM2_CH2_2                                             |

| 7 11          | 16 16  |       |      | PA2                                      | I/O/A -               |                  | PA2                              | USART2_TX/TIM5_CH3<br>ADC_IN2/TIM2_CH3<br>OPA2_OUT0              | TIM2_CH3_1                                             |

|               | 17     |       |      | VIO_4                                    | P                     | =                | VIO_4                            |                                                                  |                                                        |

|               | 18     |       |      | PD4                                      | I/O F1                |                  | PD4                              |                                                                  |                                                        |

| 8 12          | 17 19  |       |      | PA3                                      | I/O/A -               |                  | PA3                              | USART2_RX/TIM5_CH4 ADC_IN3/TIM2_CH4 OPA1_OUT0                    | TIM2_CH4_1                                             |

| 1             | 8      |       |      | VSS_4                                    | Р                     | -                | VSS_4                            |                                                                  |                                                        |

| 1             | 9 -    |       |      | VDD_IO_4                                 | Р                     | ÷                | VDD_IO_4                         |                                                                  |                                                        |

| 9 13          | 20 20  |       |      | PA4                                      | I/O/A -               |                  | PA4                              | SPI1_NSS/USART2_CK<br>ADC_IN4/OPA2_OUT1                          |                                                        |

| 10 1          | 4 21 2 | 1     |      | PA5                                      | I/O/A -               |                  | PA5                              | SPI1_SCK/ADC_IN5                                                 |                                                        |

|       | Pin N   | umber      |    |                                |         | Ø                |                             |                                           |                                         |

|-------|---------|------------|----|--------------------------------|---------|------------------|-----------------------------|-------------------------------------------|-----------------------------------------|

| QFI   | l28 QF  | <b>N48</b> | QI | Pinout<br><sub>-N68</sub> name | type    | electricity flat | Main Function (After reset) | Default multiplexing funct                | ion remapping function (8)              |

|       |         |            |    |                                |         |                  |                             | OPA2_CH1N                                 |                                         |

| 11 1: | 5 22 2: | 2          |    | PA6                            | I/O/A - |                  | PA6                         | SPI1_MISO/ADC_IN6<br>TIM3_CH1/OPA1_CH1N   | TIM1_BKIN_1                             |

| 12 1  | 6 23 2  | В          |    | PA7                            | I/O/A - |                  | PA7                         | SPI1_MOSI/ADC_IN7<br>TIM3_CH2/OPA2_CH1P   | TIM1_CH1N_1                             |

| 2     | 4 24    |            |    | PC4                            | I/O/A - |                  | PC4                         | ADC_IN14                                  |                                         |

| 2     | 5 25    |            |    | PC5                            | I/O/A - |                  | PC5                         | ADC_IN15                                  |                                         |

| - 17  | 26 26   |            |    | PB0                            | I/O/A - |                  | PB0                         | ADC_IN8/TIM3_CH3<br>OPA1_CH1P             | TIM1_CH2N_1<br>TIM3_CH3_2<br>UART4_TX_1 |

| - 18  | 27 27   |            |    | PB1                            | I/O/A - |                  | PB1                         | ADC_IN9<br>TIM3_CH4<br>OPA1_OUT1          | TIM1_CH3N_1<br>TIM3_CH4_2<br>UART4_RX_1 |

| - 19  | 28 28   |            |    | PB2                            | I/O FT  | PB2/             | воот1                       |                                           |                                         |

| - 20  | 29 29   |            |    | PB10                           | I/O/A F | Т                | PB10                        | I2C2_SCL/USART3_TX<br>OPA2_CH0N           | TIM2_CH3_2<br>TIM2_CH3_3                |

| - 21  | 30 30   |            |    | PB11                           | I/O/A F | Г                | PB11                        | I2C2_SDA/USART3_RX<br>OPA1_CH0N           | TIM2_CH4_2<br>TIM2_CH4_3                |

| 3     | 1       |            | -  | VSS_1                          | Р       |                  | VSS_1                       |                                           |                                         |

| 13 2  | 2 32 -  |            |    | VDD_IO_1                       | Р       |                  | VDD_IO_1                    |                                           |                                         |

|       | 31      |            |    | VIO_1                          | Р       |                  | VIO_1                       |                                           |                                         |

|       | 32      |            |    | VDD_1                          | Р       |                  | VDD_1                       |                                           |                                         |

|       | 33      |            |    | PD5                            | I/O FT  |                  | PD5                         |                                           |                                         |

|       | 34      |            |    | PD6                            | I/O FT  |                  | PD6                         |                                           |                                         |

| - 23  | 33 35   |            |    | PB12                           | I/O/A F | Т                | PB12                        | SPI2_NSS/I2C2_SMBA<br>USART3_CK/TIM1_BKIN |                                         |

| - 24  | 34 36   |            |    | PB13                           | I/O/A F | Г                | PB13                        | SPI2_SCK/TIM1_CH1N<br>USART3_CTS          | USART3_CTS_1                            |

| - 25  | 35 37   |            |    | PB14                           | I/O/A F | Г                | PB14                        | SPI2_MISO/TIM1_CH2N USART3_RTS/OPA2_CH0P  | USART3_RTS_1                            |

| - 26  | 36 38   |            |    | PB15                           | I/O/A F | Г                | PB15                        | SPI2_MOSI/TIM1_CH3N<br>OPA1_CH0P          |                                         |

| 14 -  | 37 39   |            |    | PC6                            | I/O FT  |                  | PC6                         | ETH_RXP                                   | TIM3_CH1_3                              |

| 15 -  | 38 40   |            |    | PC7                            | I/O FT  |                  | PC7                         | ETH_RXN                                   | TIM3_CH2_3                              |

| 16 -  | 39 41   |            |    | PC8                            | I/O FT  |                  | PC8                         | ETH_TXP                                   | TIM3_CH3_3                              |

| 17 -  | 40 42   |            |    | PC9                            | I/O FT  |                  | PC9                         | ETH_TXN                                   | TIM3_CH4_3                              |

| - 27  | 41 43   |            |    | PA8                            | I/O FT  |                  | PA8                         | USART1_CK<br>TIM1_CH1/MCO                 | USART1_CK_1<br>TIM1_CH1_1               |

| - 28  | 42 44   |            |    | PA9                            | I/O FT  |                  | PA9                         | USART1_TX<br>TIM1_CH2                     | TIM1_CH2_1                              |

|                   | Pin nı  | umber |    |      |             |          | Ø                |                             |                                      |                            |

|-------------------|---------|-------|----|------|-------------|----------|------------------|-----------------------------|--------------------------------------|----------------------------|

| QFI               | l28 QF  | N48   | QI | FN68 | pin<br>name | type (1) | electricity flat | Main Function (after reset) | Default reuse function i             | emapping function(8)       |

| - 29              | 43 45   |       |    |      | PA10        | I/O FT   |                  | PA10                        | USART1_RX<br>TIM1_CH3                | TIM1_CH3_1                 |

| 18 30             | 44 46   | •     |    |      | PA11        | I/O/A F  | Γ                | PA11                        | USART1_CTS/USBDM<br>CAN1_RX/TIM1_CH4 | USART1_CTS_1<br>TIM1_CH4_1 |

| 19 3 <sup>-</sup> | 1 45 47 | ,     |    |      | PA12        | I/O/A F  | Γ                | PA12                        | USART1_RTS/USBDP<br>CAN1_TX/TIM1_ETR | USART1_RTS_1<br>TIM1_ETR_1 |

| 20 32             | 46 48   |       |    |      | PA13        | I/O FT   |                  | SWDIO                       |                                      | PA13                       |

| - 35              | - 49    |       |    |      | VSS_2       | Р        | -                | VSS_2                       |                                      |                            |

| 21 33             | 47 50   |       |    |      | WON         | Р        | -                | WON                         |                                      |                            |

| 22 34             | 48 51   |       |    |      | ON          | Α        | -                | ON                          |                                      |                            |

| 23 36             | 49 52   |       |    |      | PA14        | I/O FT   |                  | SWCLK                       |                                      | PA14                       |

|                   |         |       |    |      |             |          |                  |                             |                                      | TIM2_CH1_1(9)              |

|                   |         |       |    |      |             |          |                  |                             |                                      | TIM2_ETR_1(9)              |

| - 37              | 50 53   |       |    |      | PA15        | I/O FT   |                  | PA15                        |                                      | TIM2_CH1_3(9)              |

|                   |         |       |    |      |             |          |                  |                             |                                      | TIM2_ETR_3(9)              |

|                   |         |       |    |      |             |          |                  |                             |                                      | SPI1_NSS_1                 |

| 5                 | 1 54    |       |    |      | PC10        | I/O FT   |                  | PC10                        | UART4_TX                             | USART3_TX_1                |

| 5                 | 2 55    |       |    |      | PC11        | I/O FT   |                  | PC11                        | UART4_RX                             | USART3_RX_1                |

| 5                 | 3 56    |       |    |      | PC12        | I/O FT   |                  | PC12                        |                                      | USART3_CK_1                |

| 5                 | 4 57    |       |    |      | PD2         | I/O FT   |                  | PD2                         | TIM3_ETR                             | TIM3_ETR_2                 |

|                   |         |       |    |      |             |          |                  |                             |                                      | TIM3_ETR_3                 |

|                   |         |       |    |      |             |          |                  |                             |                                      | TIM2_CH2_1                 |

| - 38              | 55 58   |       |    |      | PB3         | I/O FT   |                  | PB3                         |                                      | TIM2_CH2_3                 |

|                   |         |       |    |      |             |          |                  |                             |                                      | SPI1_SCK_1                 |

| - 39              | 56 59   |       |    |      | PB4         | I/O FT   |                  | PB4                         |                                      | TIM3_CH1_2                 |

|                   |         |       |    |      |             |          |                  |                             |                                      | SPI1_MISO_1                |

| - 40              | 57 60   |       |    |      | PB5         | I/O FT   |                  | PB5                         | 2C1_SMBA                             | TIM3_CH2_2                 |

|                   |         |       |    | 5    |             |          |                  |                             | 1204 801                             | SPI1_MOSI_1                |

| 24 41             | 58 61   |       |    |      | PB6         | I/O FT   |                  | PB6                         | I2C1_SCL<br>TIM4_CH1/USBFS_DM        | USART1_TX_1                |

| 25 42             | 59 62   |       |    |      | PB7         | I/O FT   |                  | РВ7                         | I2C1_SDA<br>TIM4_CH2/USBFS_DP        | USART1_RX_1                |

|                   | 43 6    | 63    |    |      | воото       | 1        | ·                | воото                       |                                      |                            |

| 26(6)             | 44 6    | 1 64  |    |      | PB8         | I/O/A F  | Г                | PB8                         | TIM4_CH3                             | I2C1_SCL_1                 |

| $\vdash$          |         |       |    |      |             |          |                  |                             |                                      | /CAN1_RX_2                 |

| - 45              | 62 65   |       |    |      | PB9         | I/O/A F  | r                | PB9                         | TIM4_CH4                             | I2C1_SDA_1                 |

|                   | 66      |       |    |      | PD3         | I/O FT   |                  | PD3                         |                                      | /CAN1_TX_2                 |

| - 46              | 63 -    |       |    |      | VSS_3       | P        | -                | VSS_3                       |                                      |                            |

| 27 47             |         |       |    |      | VDD_IO_3    | Р        | -                | VDD_IO_3                    |                                      |                            |

|                   |         |       |    |      |             |          |                  |                             |                                      |                            |

| QF | Pin Nu | mber | QI | Pinout<br>name | pin<br>type | olectricity flat | Main function (After reset) | ion remapping function (8) |

|----|--------|------|----|----------------|-------------|------------------|-----------------------------|----------------------------|

|    | 67     |      |    | VIO_3          | Р           | -                | VIO_3                       |                            |

|    | - 68   |      |    | VDD_3          | Р           | ÷                | VDD_3                       |                            |

Note 1: Explanation of table abbreviations

- = TTL/CMOS level Schmitt input; O = CMOS Level three-state output; \$\bar{A}\$ Analog signal input or output;

- P = power supply; 1511/ tolerant; = RF signal input and output (antenna);

ANT Note 2: PC13, PC14 and PC15 pins are powered through a power switch that can only sink a limited current (3mA).

Can be used as TAMPER pin, RTC alarm or seconds outputPC14 and PC15 can only be used as LSE pins;

When used as an output pin, it can only work in 2MHz mode, the maximum driving load is 30pF, and cannot be used as a current source (such as driving LED)

Note 8: The value after the underline of the remapping function indicARSIME ARRIVIFation value of the corresponding bit in the register. For example: UART4\_RX\_@eans

The corresponding bit of the register is configured as 11b;

Note  $\mathbf{GiaT1M2}_{\underline{c}}\mathbf{GHA}\mathbf{A}\mathbf{a}\mathbf{nd}\mathbf{e}$  same pin, but cannot be used at the same time.

Machine Translated by Google

CH32V208 Datasheet http://wch.cn

#### 3.3 Pin alternate function

Note that the pin function descriptions in the table below are for all functions and do not involve specific models. Please confirm whether this function is available according to the product model resource table before checking

Table 3-2 Pin multiplexing and remapping functions

| Reuse | ADC     | ТІМ1                   | TIM2/3/4/5                                                   | UART/USART                 | USB      | sys   | 2C         | SPI         | ЕТН | ОРА       | CAN       |

|-------|---------|------------------------|--------------------------------------------------------------|----------------------------|----------|-------|------------|-------------|-----|-----------|-----------|

| PAO   | ADC_IN0 |                        | TIM2_CH1<br>TIM2_ETR<br>TIM2_CH1_2<br>TIM2_ETR_2<br>TIM5_CH1 | USART2_CTS                 |          | BUYIN |            |             |     |           |           |

| PA1   | ADC_IN1 |                        | TIM2_CH2<br>TIM2_CH2_2<br>TIM5_CH2                           | USART2_RTS                 |          |       |            |             |     |           |           |

| PA2   | ADC_IN2 |                        | TIM2_CH3<br>TIM2_CH3_1<br>TIM5_CH3                           | USART2_TX                  |          |       |            |             |     | OPA2_OUT0 |           |

| PA3   | ADC_IN3 |                        | TIM2_CH4<br>TIM2_CH4_1<br>TIM5_CH4                           | USART2_RX                  |          |       |            |             |     | OPA1_OUT0 |           |

| PA4   | ADC_IN4 |                        |                                                              | USART2_CK                  |          |       |            | SPI1_NSS    |     | OPA2_OUT1 |           |

| PA5   | ADC_IN5 |                        |                                                              |                            |          |       |            | SPI1_SCK    |     | OPA2_CH1N |           |

| PA6   | ADC_IN6 | TIM1_BKIN_1            | TIM3_CH1                                                     |                            |          |       |            | SPI1_MISO   |     | OPA1_CH1N |           |

| PA7   | ADC_IN7 | TIM1_CH1N_1            | TIM3_CH2                                                     |                            |          |       |            | SPI1_MOSI   |     | OPA2_CH1P |           |

| PA8   |         | TIM1_CH1<br>TIM1_CH1_1 |                                                              | USART1_CK<br>USART1_CK_1   |          | мсо   |            |             |     |           |           |

| PA9   |         | TIM1_CH2<br>TIM1_CH2_1 |                                                              | USART1_TX                  |          |       |            |             |     |           |           |

| PA10  |         | TIM1_CH3<br>TIM1_CH3_1 |                                                              | USART1_RX                  |          |       |            |             |     |           |           |

| PA11  |         | TIM1_CH4<br>TIM1_CH4_1 |                                                              | USART1_CTS<br>USART1_CTS_1 | USBDM    |       |            |             |     |           | CAN1_RX   |

| PA12  |         | TIM1_ETR TIM1_ETR_1    |                                                              | USART1_RTS<br>USART1_RTS_1 | USBDP    |       |            |             |     |           | CAN1_TX   |

| PA13  |         |                        |                                                              |                            |          | SWDIO |            |             |     |           |           |

| PA14  |         |                        |                                                              |                            |          | SWCLK |            |             |     |           |           |

| PA15  |         |                        | TIM2_CH1_1<br>TIM2_ETR_1<br>TIM2_CH1_3<br>TIM2_ETR_3         |                            |          |       |            | SPI1_NSS_1  |     |           |           |

| PB0   | ADC_IN8 | TIM1_CH2N_1            | TIM3_CH3<br>TIM3_CH3_2                                       | UART4_TX_1                 |          |       |            |             | 8   | OPA1_CH1P |           |

| PB1   | ADC_IN9 | TIM1_CH3N_1            | TIM3_CH4<br>TIM3_CH4_2                                       | UART4_RX_1                 |          |       |            |             |     | OPA1_OUT1 |           |

| PB2   |         |                        |                                                              |                            |          | BOOT1 |            |             |     |           |           |

| PB3   |         |                        | TIM2_CH2_1<br>TIM2_CH2_3                                     |                            |          |       |            | SPI1_SCK_1  |     |           |           |

| PB4   |         |                        | TIM3_CH1_2                                                   |                            |          |       |            | SPI1_MISO_1 |     |           |           |

| PB5   |         |                        | TIM3_CH2_2                                                   |                            |          |       | 2C1_SMBA   | SPI1_MOSI_1 |     |           |           |

| PB6   |         |                        | TIM4_CH1                                                     | USART1_TX_1                | USBFS_DM |       | I2C1_SCL   |             | 0   |           |           |

| PB7   |         |                        | TIM4_CH2                                                     | USART1_RX_1                | USBFS_DP |       | I2C1_SDA   |             | 9   |           |           |

| PB8   |         |                        | TIM4_CH3                                                     |                            |          |       | I2C1_SCL_1 |             |     |           | CAN1_RX_2 |