B2B GST Credit Available

- Stock: 0 in Stock

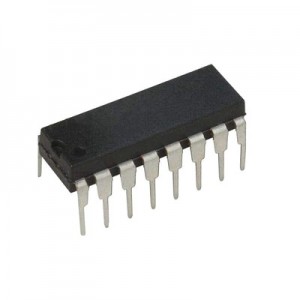

- SKU: 01105

- Delivery Time

- Bulk & B2B RFQ

74HC107 Dual JK Flip Flop with Reset, Negative Edge Trigger , NXP Semiconductor (Philips)

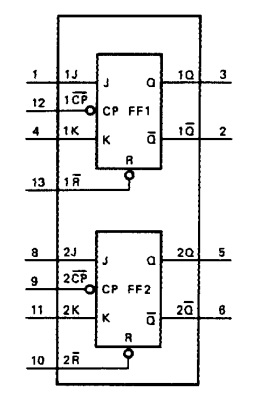

The 74HC/HCT107 are dual negative-edge triggered JK-type flip-flops featuring individual J, K, clock (nCP) and reset (nR) inputs; also complementary Q and Q outputs. The J and K inputs must be stable one set-up time prior to the HIGH-to-LOW clock transition for predictable operation.

The reset (nR) is an asynchronous active LOW input. When LOW, it overrides the clock and data inputs, forcing the Q output LOW and the Q output HIGH. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

The 74HC/HCT107 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL).

IMPORTANT NOTICE

All products sold at HUBTRONICS are 100% Genuine parts made by the original manufacturers as listed on the product page. We do not stock duplicate parts in any case. All goods are checked before sending them out. The user assumes all responsibility and liability for proper and safe handling of the goods after receiving the shipment. For any further clarification you can contact us by the means provided on the contact us page.