B2B GST Credit Available

- Stock: 0 in Stock

- SKU: 04234

- Delivery Time

- Bulk & B2B RFQ

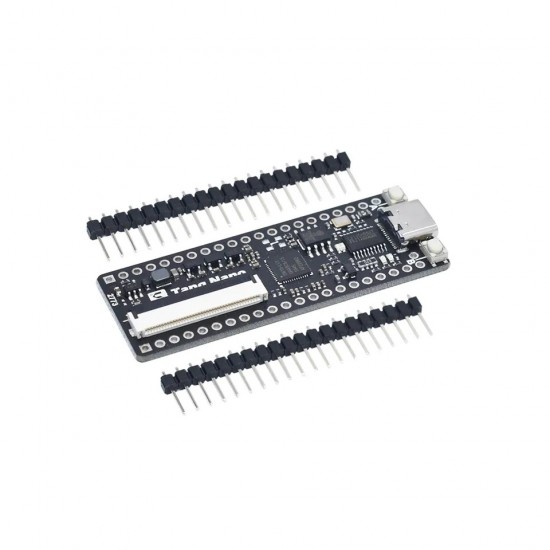

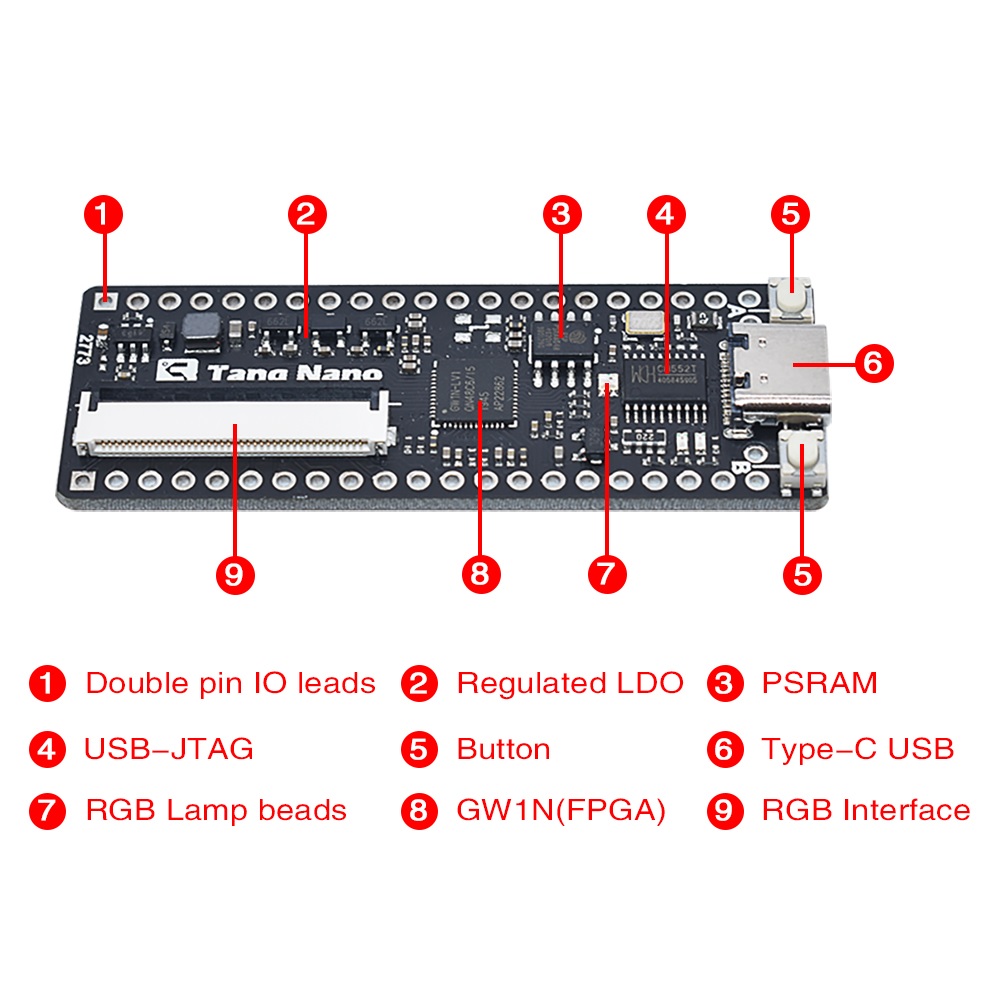

Sipeed Lichee Tang Nano minimalist line FPGA development board

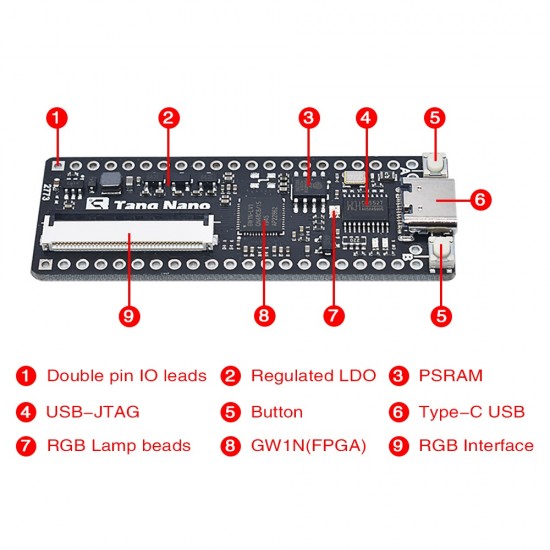

Lichee Tang Nano series is Bee simple GW1N-1 FPGA development board based on a high cloud semiconductor design. Compact design delicate boards, chips all resources are drawn onboard Type-C, USB-JTAG, PSRAM, RGB (LCD screen can be accessed, VGA and other peripherals), etc., and all IO resources leads, convenient developer expand the use, ideal for small digital logic design and experiment.

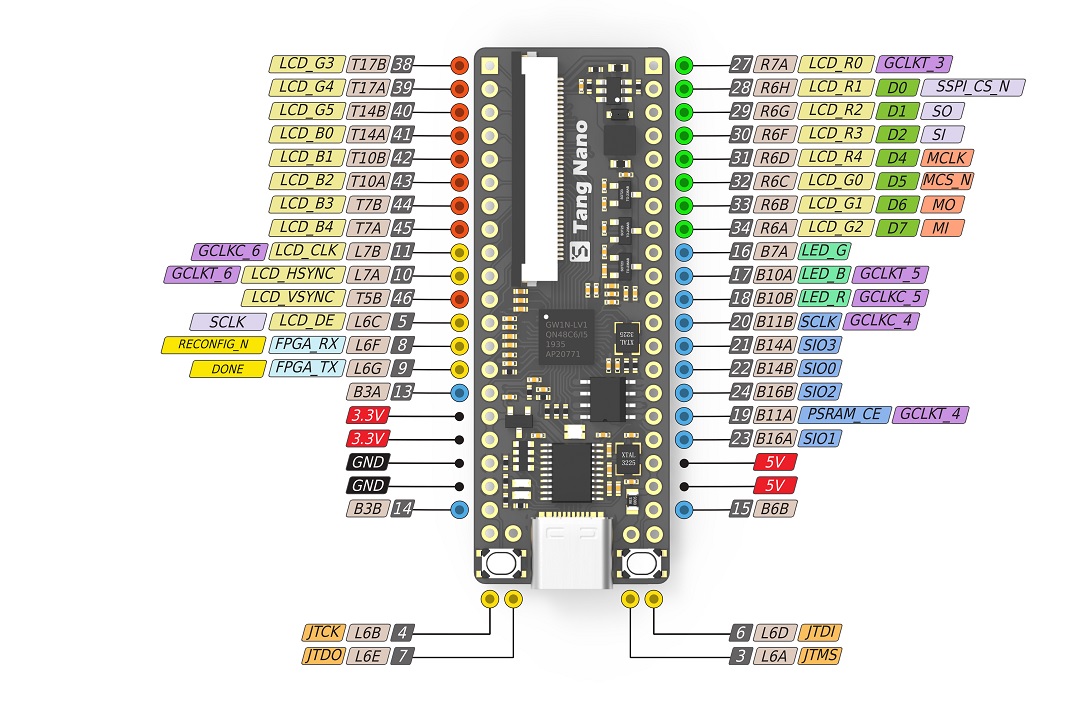

The main features for the Tang Nano FPGA Board include 34 rich I/O PINs and a USB Type-C interface. This allows for the power supply and downloading code. Additionally, the JTAG downloader supports a USB cable, enabling code to be downloaded without an extra downloader outside the board. A 40 Pin FPC LCD carrier allows a 40 PIN RGB LCD Screen to be equipped on the board.

Features

- GW1N-1-LV:1152 LUT4, 864 FF(Flip-Flop)

- 72K B-SRAM(bits); 96K user flash(bits); 1 PLL

- Support a 5 inches 800*480 screen

- Onboard JTAG Downloader

- Small size, low cost

Specifications

- FPGA chip GWIN-1-LV: LUT4 1152, Flip-Flop 864, BSRAM(bits) 72K, USER Flash(bits) 96K, PLLs+DLLs 1+0, Core voltage 1.2V

- Download method: Simply plug in the USB cable and download it via the onboard downloader.

- Power circuit: Each Bank occupies a separate LDO power chip (except BANK0/3). Adjust the I/O level of BANK1 and BANK2 by replacing the LDO chip by yourself.

- 40P FPC LCD carrier: Standard 40 RGB LCD interface. On-board screen backlight driver circuit(default normally open, EN pin can be connected to FPGA)

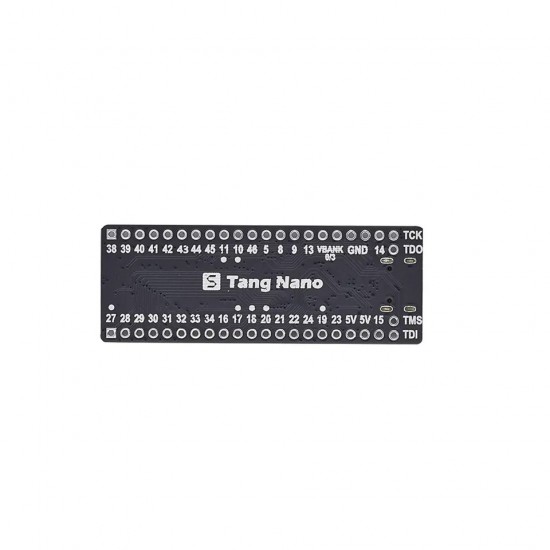

- I/O: 34 I/O ports and multiple power pins on both sides. Both sides of the pins can be directly inserted into the breadboard.

- Onboard PSRAM chip: Capacity: 64Mbits Voltage: 3.3V

- Power supply and download interface: USB-Type-C interface

- RGB LED: Onboard small size RGB LED

- Button: 2 3X4mm buttons onboard

- Crystal oscillator: Onboard 24Mhz crystal oscillator(started by CH552)

- External supply voltage demand: 5.0V±0.2V

- External supply current demand: >400mA@5V

- Temperature rise: <30K

- Range of working temperature: −30°C~50°C

Pin Daigram